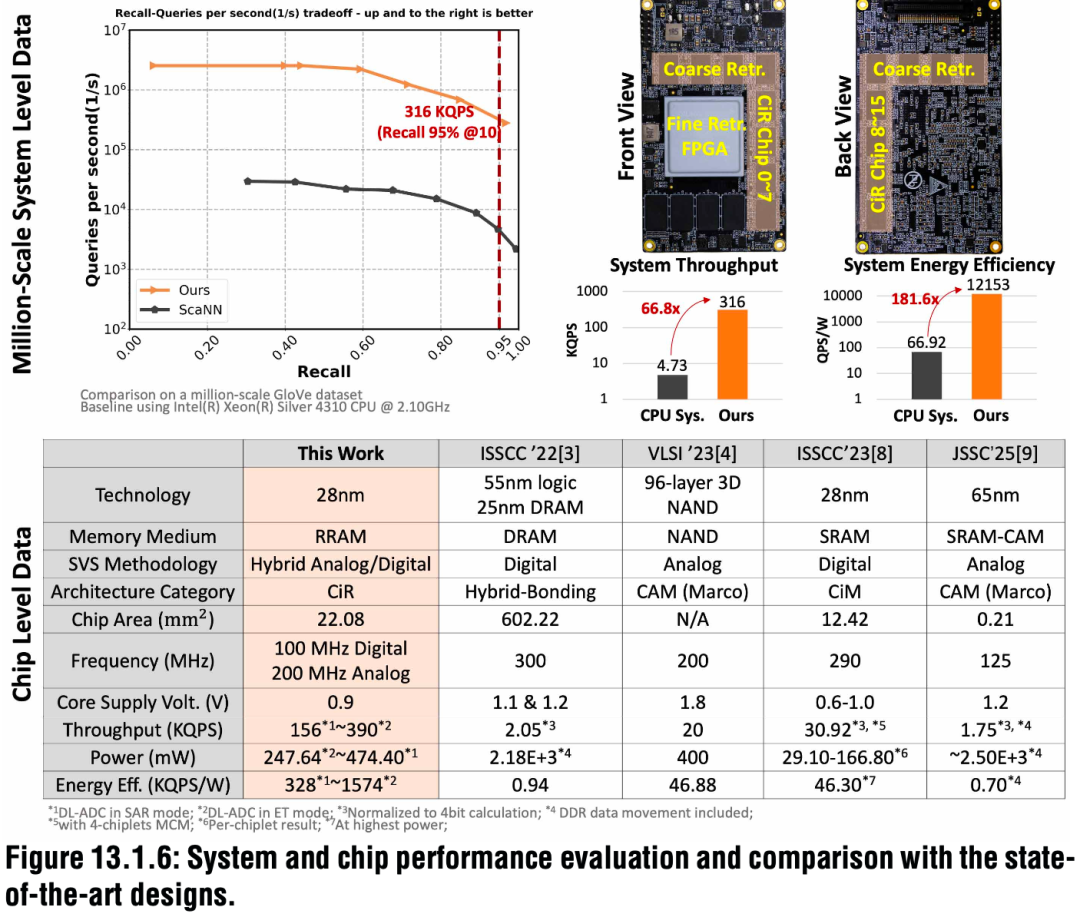

在2026年国际固态电路大会(ISSCC 2026)上,清华大学、华为、字节跳动联合发布的基于HYDAR框架的28nm混合存内计算(CiR)芯片,以RRAM为核心载体,通过DL-ADC早期终止、PPSP调度流水线等核心优化实力强大的配资公司,实现了高吞吐、高能效与高精度的平衡,其单芯片390K QPS吞吐率、1574K QPS/W能效比,以及多芯片扩展后66倍QPS提升的性能表现,为推荐系统算力瓶颈突破提供了全新解决方案。

相较于传统DRAM、NAND TCAM加速器的固有缺陷,该芯片的技术突破不仅补齐了行业短板,更精准契合当下数字经济对高效算力的核心需求,具备广阔的市场落地空间与行业赋能价值。

| 精准匹配高算力需求领域

推荐系统作为连接用户与海量内容的核心枢纽,已深度渗透至电商、流媒体、社交、广告等关键领域,而相似向量检索(SVS)的效率直接决定推荐体验与运营成本,这也是CiR芯片的核心落地场景。结合芯片性能优势与行业需求,其市场应用可聚焦三大核心领域,且均具备极强的落地可行性。

破解大规模推荐算力瓶颈

当前互联网平台正面临用户规模激增、内容体量爆炸式增长的挑战,以电商、短视频、直播平台为代表,需在毫秒级响应时间内,从数十亿甚至百亿级向量库中完成用户兴趣匹配,传统算力架构已难以支撑。例如,快手等短视频平台需承载高峰期每秒数十万并发调用,从上百亿级短视频库中完成精准推荐,其推荐系统的存储与计算压力巨大,而CiR芯片通过多芯片扩展可实现百万级实时端到端推荐,恰好适配这一需求。

对于字节跳动、阿里巴巴、腾讯等互联网巨头而言,CiR芯片可直接替换现有低效加速器,在保证推荐准确率与CPU相当的前提下,将QPS提升66倍、能效提升181倍,大幅降低数据中心的算力成本与能耗。同时,芯片的大规模扩展能力的可适配不同平台的业务规模,无论是中小平台的轻量化推荐需求,还是巨头的超大规模向量检索场景,均能实现性能与成本的最优平衡,具备极强的场景适配性。此外,生成式推荐的兴起进一步提升了对算力的需求,CiR芯片的高吞吐特性可支撑生成式推荐模型的快速推理,助力平台构建“内容-推荐-广告”的协同闭环,提升广告转化效率。

赋能高并行计算任务落地

随着AI大模型应用的爆发式增长,数据处理的并行度需求持续提升,存算一体技术已成为突破冯·诺依曼架构“内存墙”瓶颈的关键路径。CiR芯片基于RRAM的存内计算特性,最大限度减少数据移动,并行度优势显著,除推荐系统外,还可延伸至AI推理、大数据检索、图像识别等高并行计算场景。例如,在AI大模型的边缘推理场景中,芯片的高能效比的可降低设备功耗,适配终端设备的算力需求;在大数据检索场景中,两步由粗到细的检索架构可实现高效数据筛选,大幅提升检索效率。

根据弗若斯特沙利文预测,2029年中国AI芯片市场规模将激增至1.34万亿元,年复合增长率达53.7%,而存算一体芯片作为AI算力的核心支撑,市场需求将持续释放。CiR芯片凭借28nm成熟工艺的成本优势,相较于高端制程芯片更易实现规模化量产,可快速切入AI算力市场,填补中高端加速器的市场空白,尤其适配中小企业的AI算力需求,助力AI技术的普惠落地。

适配边缘端高效算力需求

工业互联网、物联网的快速发展,推动算力需求向边缘端延伸,边缘设备对算力、功耗、体积的综合要求极高,传统芯片难以兼顾性能与能耗。CiR芯片的高能效比(1574K QPS/W)与小型化潜力,可适配工业物联网中的设备状态监测、智能调度,以及消费物联网中的个性化推荐、智能交互等场景。例如,在工业生产中的设备故障预警系统中,芯片可快速处理海量传感器数据,实现实时检索与分析,提升预警响应速度;在智能家居设备中,可支撑本地个性化推荐算法的高效运行,降低设备功耗,提升用户体验。

此外,RRAM作为存算一体的核心技术路径,具备非易失性、低功耗、高密度的优势,随着3D堆叠技术的成熟,CiR芯片的存储密度与性能将进一步提升,可适配更多边缘端高算力场景,成为边缘计算的核心算力支撑。

| 乘算力东风,重构推荐系统算力格局

当前,数字经济的持续发展推动推荐系统向“更实时、更精准、更高效”升级,算力需求呈现爆发式增长,同时存算一体技术成为行业发展的核心趋势,CiR芯片凭借技术、成本、场景三大优势,有望在未来3-5年实现规模化落地,重构推荐系统算力架构,推动行业进入高效算力新时代。

引领存算一体在推荐领域的规模化应用

存算一体技术已被公认为深度学习加速的极具前景的技术路线,而RRAM作为核心存储介质,正成为行业布局的重点。目前,台积电、三星、美光等全球芯片巨头均在积极布局RRAM技术,国内企业如铭芯启睿等也凭借中科院的技术积累实现快速突破,已完成产品工程批验证流片,为RRAM技术的产业化奠定了基础。

本次发布的CiR芯片,首次将RRAM存内计算技术与推荐系统深度结合,解决了存算一体应用于相似向量检索的核心痛点,其DL-ADC早期终止、PPSP调度等优化方案,为行业提供了可复用的技术范式。未来,随着芯片工艺的迭代(如向14nm及以下制程升级),以及多芯片扩展技术的完善,其性能将进一步提升,同时成本将持续降低,推动存算一体技术在推荐系统领域的规模化应用,逐步替代传统CPU、GPU及低效加速器,成为推荐系统的核心算力载体。此外,产学研协同创新模式(如清华大学、华为、字节跳动的联合研发)将加速技术迭代,推动更多核心技术突破,提升行业整体技术水平。

千亿级赛道,增长潜力持续释放

从市场规模来看,推荐系统加速器市场是AI芯片市场的重要细分领域,随着互联网、AI、物联网的深度融合,市场需求将持续扩容。一方面,互联网平台的推荐系统升级需求迫切,国内电商、短视频、社交平台的数量众多,仅头部平台的算力升级需求就足以支撑芯片的初期市场规模;另一方面,AI大模型与推荐系统的结合,将进一步提升算力需求,推动加速器市场的快速增长。

同时,存算一体技术的整体市场规模也在快速扩大,根据QYResearch数据,2024年全球存算一体技术市场规模达2.68亿美元,预计2031年将突破54亿美元,年复合增长率达42.7%。CiR芯片作为存算一体技术在推荐领域的标杆性产品,可依托技术优势抢占市场份额,同时向其他高并行计算场景延伸,进一步扩大市场覆盖范围。此外,国家产业资本对RRAM等新型存储技术的认可与支持,也将为芯片的市场推广提供有力保障,加速市场渗透。

产学研协同,打造核心竞争力

当前,推荐系统加速器市场呈现“三足鼎立”的竞争格局,传统SEO转型企业、通用AIGC工具厂商、垂直领域服务商各有优势,但均存在技术短板。CiR芯片的推出,凭借“高吞吐、高能效、高精度”的差异化优势,打破了现有竞争格局,尤其在大规模实时推荐场景中,具备不可替代的竞争力。

从竞争优势来看,研发团队的产学研背景(高校+科技巨头)为芯片的技术迭代与场景落地提供了双重保障:清华大学的科研实力支撑核心技术突破,华为、字节跳动的产业资源则可推动芯片的场景验证与规模化应用,这种协同模式将成为芯片的核心竞争力。此外,28nm成熟工艺的采用,使得芯片相较于高端制程芯片更易实现量产,成本优势显著,可快速切入中高端市场,同时避免了高端制程芯片的产能瓶颈与成本压力。

未来,随着更多企业布局存算一体推荐加速器,市场竞争将逐步加剧,但具备技术壁垒、场景优势与量产能力的企业将占据主导地位。CiR芯片的研发团队可通过持续的技术迭代、场景深耕与产业链合作,进一步巩固优势,同时推动行业标准的建立,引领行业健康发展。

潜在挑战与应对方向

尽管CiR芯片具备广阔的市场前景,但在规模化落地过程中仍面临一些潜在挑战:一是生态适配问题,现有推荐系统的软硬件架构多基于传统算力设备设计,芯片的落地需要进行软硬件适配改造,增加了企业的迁移成本;二是产业链协同问题,RRAM存内计算技术的规模化应用,需要芯片设计、制造、封装测试等环节的协同配合,目前国内产业链仍需进一步完善;三是技术竞争问题,全球芯片巨头的布局将加剧技术竞争,核心技术的迭代速度将直接影响芯片的市场竞争力。

针对上述挑战,可通过三大方向应对:一是联合互联网平台、软件厂商打造适配生态,提供一站式软硬件解决方案,降低企业迁移成本,如快手基于异构存储的推荐系统改造经验,可为CiR芯片的场景落地提供参考;二是深化产学研协同与产业链合作,联合芯片制造企业(如中芯国际)提升量产能力,同时推动核心技术的专利布局,构建技术壁垒;三是持续加大研发投入,聚焦制程升级、性能优化与场景延伸,提升芯片的综合竞争力,应对全球技术竞争。

| 总结

基于HYDAR框架的CiR芯片,是存算一体技术与推荐系统深度融合的重要突破,其核心价值在于破解了传统推荐系统算力瓶颈,实现了性能、能效与精度的平衡,精准契合数字经济时代的算力需求。从市场应用来看,芯片可深度适配互联网、AI、工业物联网等多领域的高算力场景,落地可行性强;从行业前景来看,依托技术迭代、市场扩容与产学研协同优势,芯片有望在千亿级算力赛道中占据重要地位,推动推荐系统算力架构的重构,同时助力存算一体技术的产业化落地。

未来,随着技术的持续迭代与场景的不断延伸,CiR芯片不仅将成为推荐系统的核心算力支撑,更将赋能更多高并行计算场景,为数字经济的高质量发展注入新动能,同时推动我国在存算一体芯片领域的技术突破与产业升级实力强大的配资公司,提升在全球芯片产业中的核心竞争力。

红启网提示:文章来自网络,不代表本站观点。